著名医師による解説が無料で読めます

すると翻訳の精度が向上します

このホワイトペーパーでは、新しいスパイクカウントベースの方法に基づいて、エネルギーと面積効率の高いスパイクニューラルネットワーク(SNN)プロセッサを紹介します。低コストのSNN設計のために、学習モードと推測操作モードの両方のために、ハードウェアに優しい複雑さ削減技術を提案します。まず、監視されていない学習プロセスでは、スパイクカウントベースの学習方法を提案します。新しい学習アプローチでは、シナプス後およびシナプス後のスパイク数を利用して、シナプス重量のビット幅と重量の更新数を減らします。エネルギー効率の高い推論操作については、事前定義されたスパイクの数に達するまで、各入力軸索の入力スパイクの数が即時膜の更新なしで蓄積される蓄積ベースのコンピューティングスキームを提案します。さらに、計算スキップスキームは意味のない計算を識別し、それらをスキップしてエネルギー効率を向上させます。提案されている低複雑さの設計手法に基づいて、65 nm CMOSプロセスを使用してSNNプロセッサを設計および実装します。実装の結果によると、SNNプロセッサは、400の興奮性ニューロンを備えた1ビット230 Kシナプスウェイトのみを使用して、MNISTデータセットで認識精度の87.4%を達成します。エネルギー消費量は、推測モードで0.26 PJ/SOPおよび0.31μJ/推論、学習モードでは1.42 PJ/SOPおよび2.63μJ/学習です。

このホワイトペーパーでは、新しいスパイクカウントベースの方法に基づいて、エネルギーと面積効率の高いスパイクニューラルネットワーク(SNN)プロセッサを紹介します。低コストのSNN設計のために、学習モードと推測操作モードの両方のために、ハードウェアに優しい複雑さ削減技術を提案します。まず、監視されていない学習プロセスでは、スパイクカウントベースの学習方法を提案します。新しい学習アプローチでは、シナプス後およびシナプス後のスパイク数を利用して、シナプス重量のビット幅と重量の更新数を減らします。エネルギー効率の高い推論操作については、事前定義されたスパイクの数に達するまで、各入力軸索の入力スパイクの数が即時膜の更新なしで蓄積される蓄積ベースのコンピューティングスキームを提案します。さらに、計算スキップスキームは意味のない計算を識別し、それらをスキップしてエネルギー効率を向上させます。提案されている低複雑さの設計手法に基づいて、65 nm CMOSプロセスを使用してSNNプロセッサを設計および実装します。実装の結果によると、SNNプロセッサは、400の興奮性ニューロンを備えた1ビット230 Kシナプスウェイトのみを使用して、MNISTデータセットで認識精度の87.4%を達成します。エネルギー消費量は、推測モードで0.26 PJ/SOPおよび0.31μJ/推論、学習モードでは1.42 PJ/SOPおよび2.63μJ/学習です。

In this paper, we present an energy and area efficient spike neural network (SNN) processor based on novel spike counts based methods. For the low cost SNN design, we propose hardware-friendly complexity reduction techniques for both of learning and inferencing modes of operations. First, for the unsupervised learning process, we propose a spike counts based learning method. The novel learning approach utilizes pre- and post-synaptic spike counts to reduce the bit-width of synaptic weights as well as the number of weight updates. For the energy efficient inferencing operations, we propose an accumulation based computing scheme, where the number of input spikes for each input axon is accumulated without instant membrane updates until the pre-defined number of spikes are reached. In addition, the computation skip schemes identify meaningless computations and skip them to improve energy efficiency. Based on the proposed low complexity design techniques, we design and implement the SNN processor using 65 nm CMOS process. According to the implementation results, the SNN processor achieves 87.4% of recognition accuracy in MNIST dataset using only 1-bit 230 k synaptic weights with 400 excitatory neurons. The energy consumptions are 0.26 pJ/SOP and 0.31 μJ/inference in inferencing mode, and 1.42 pJ/SOP and 2.63 μJ/learning in learning mode of operations.

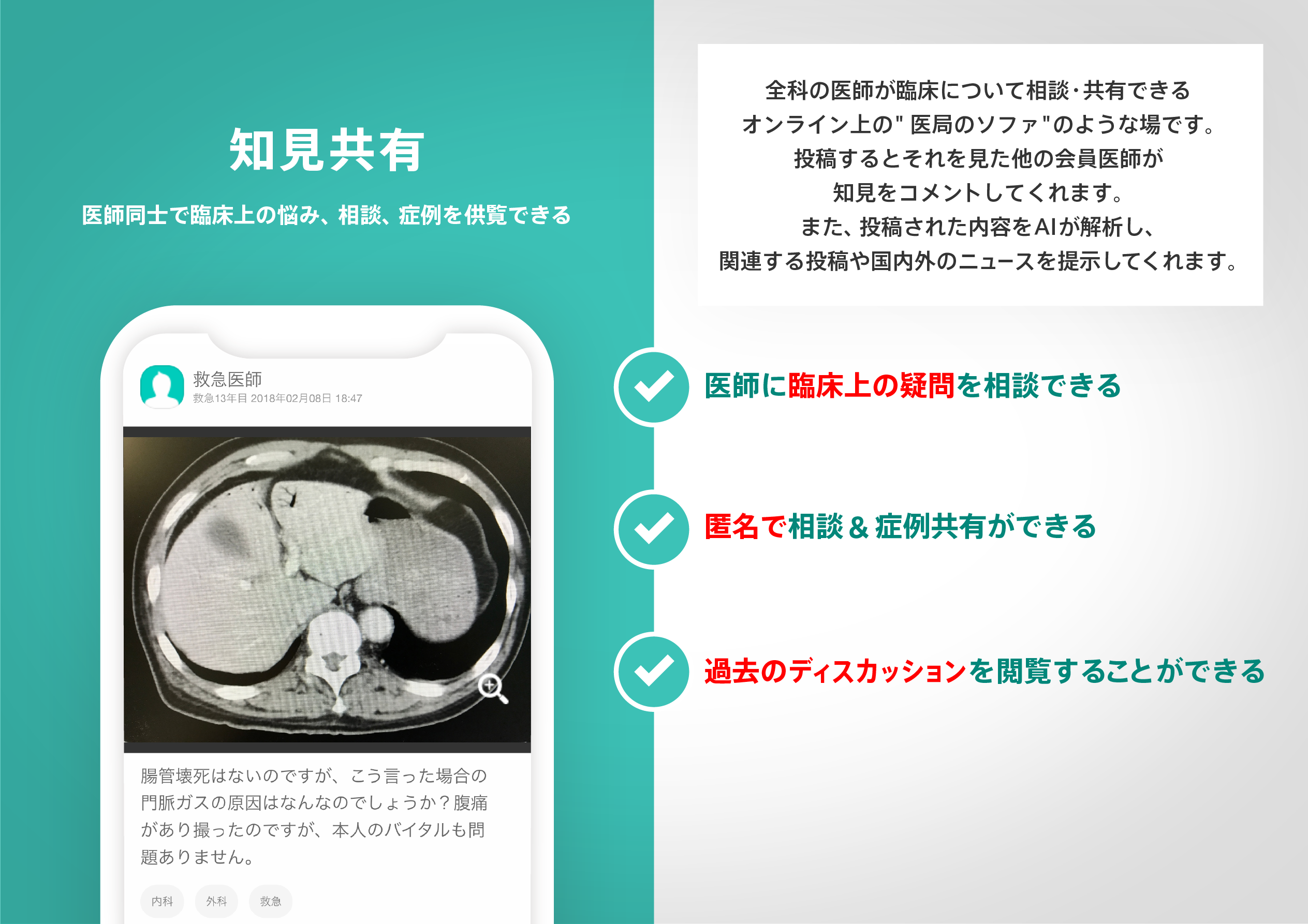

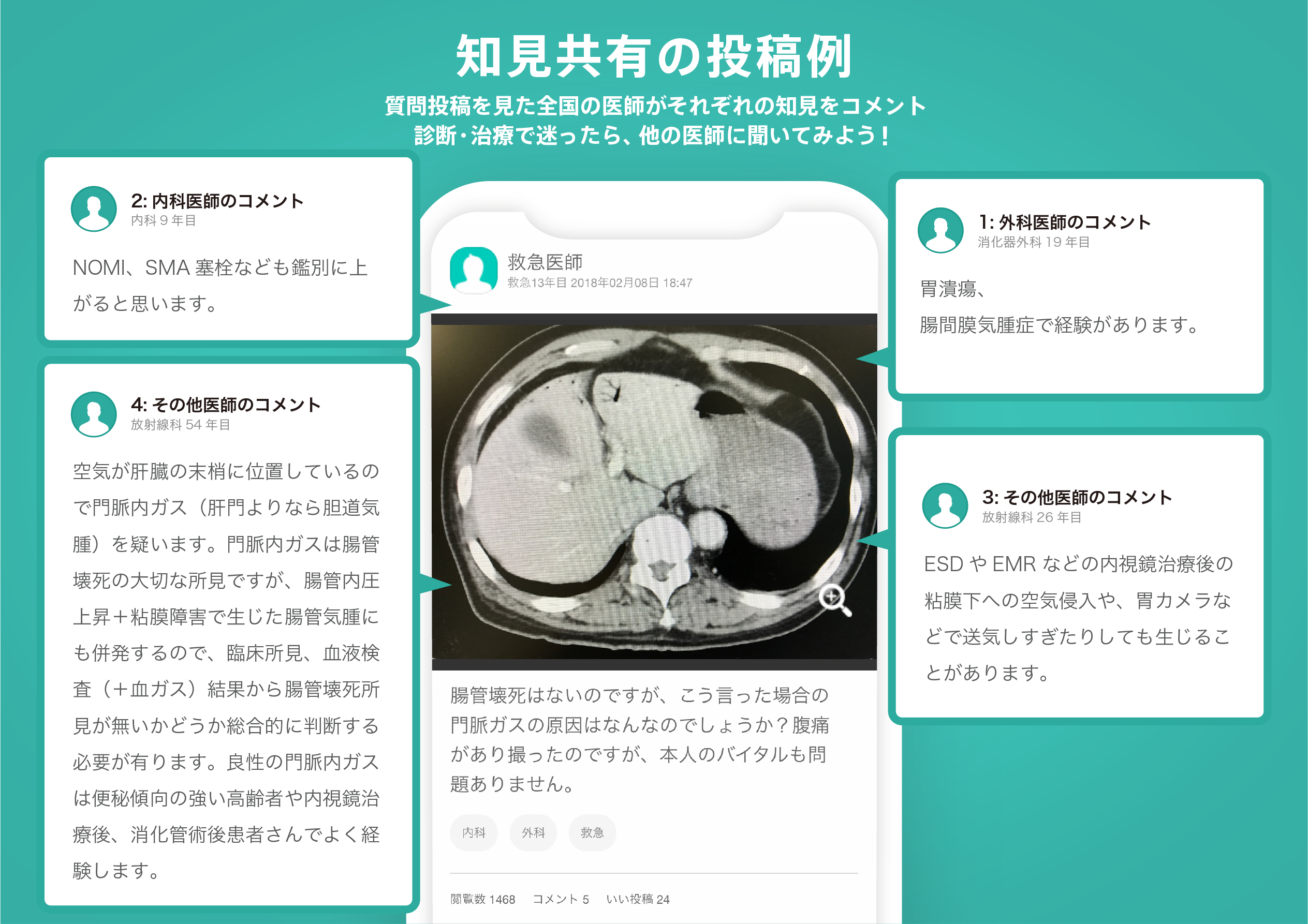

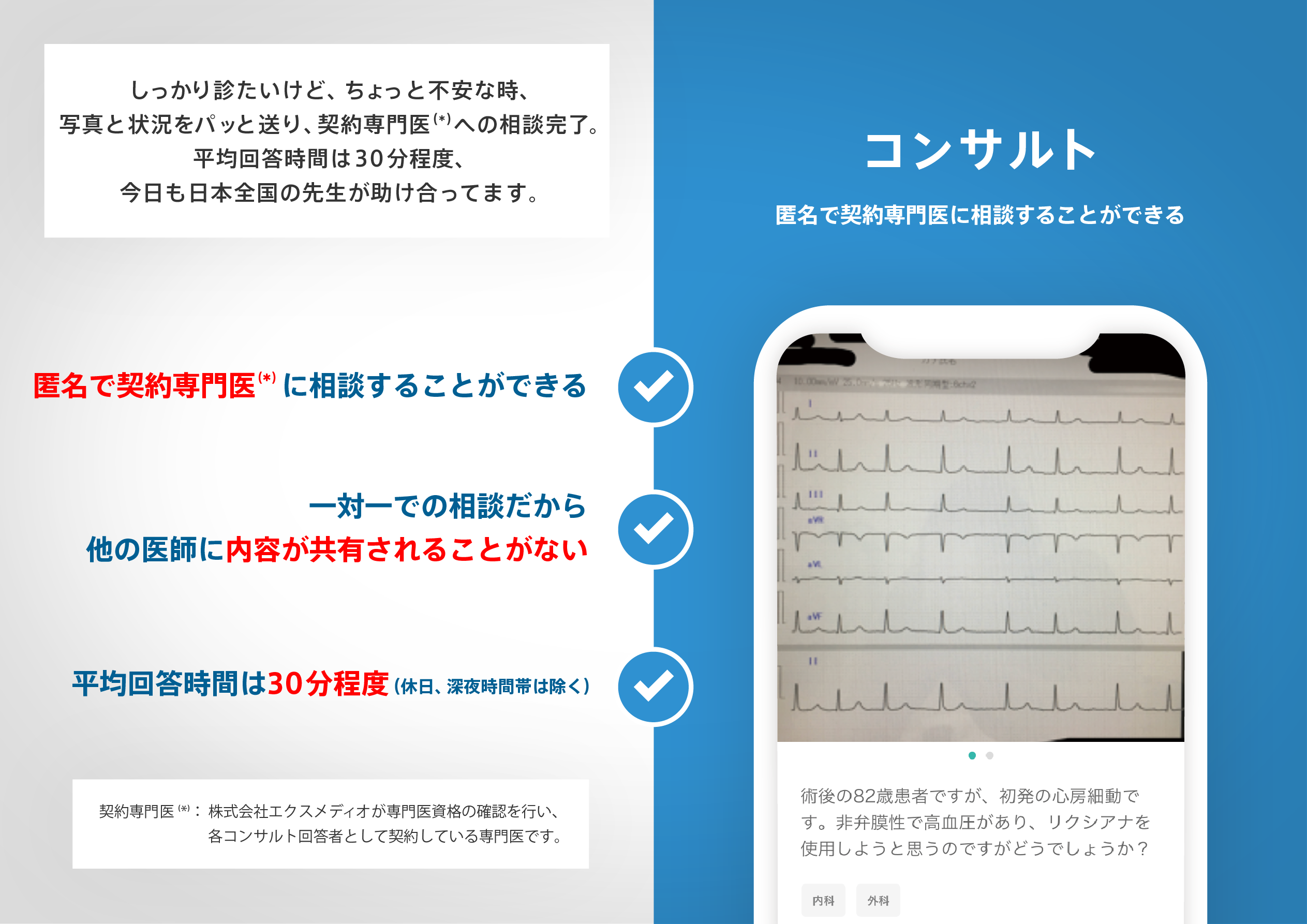

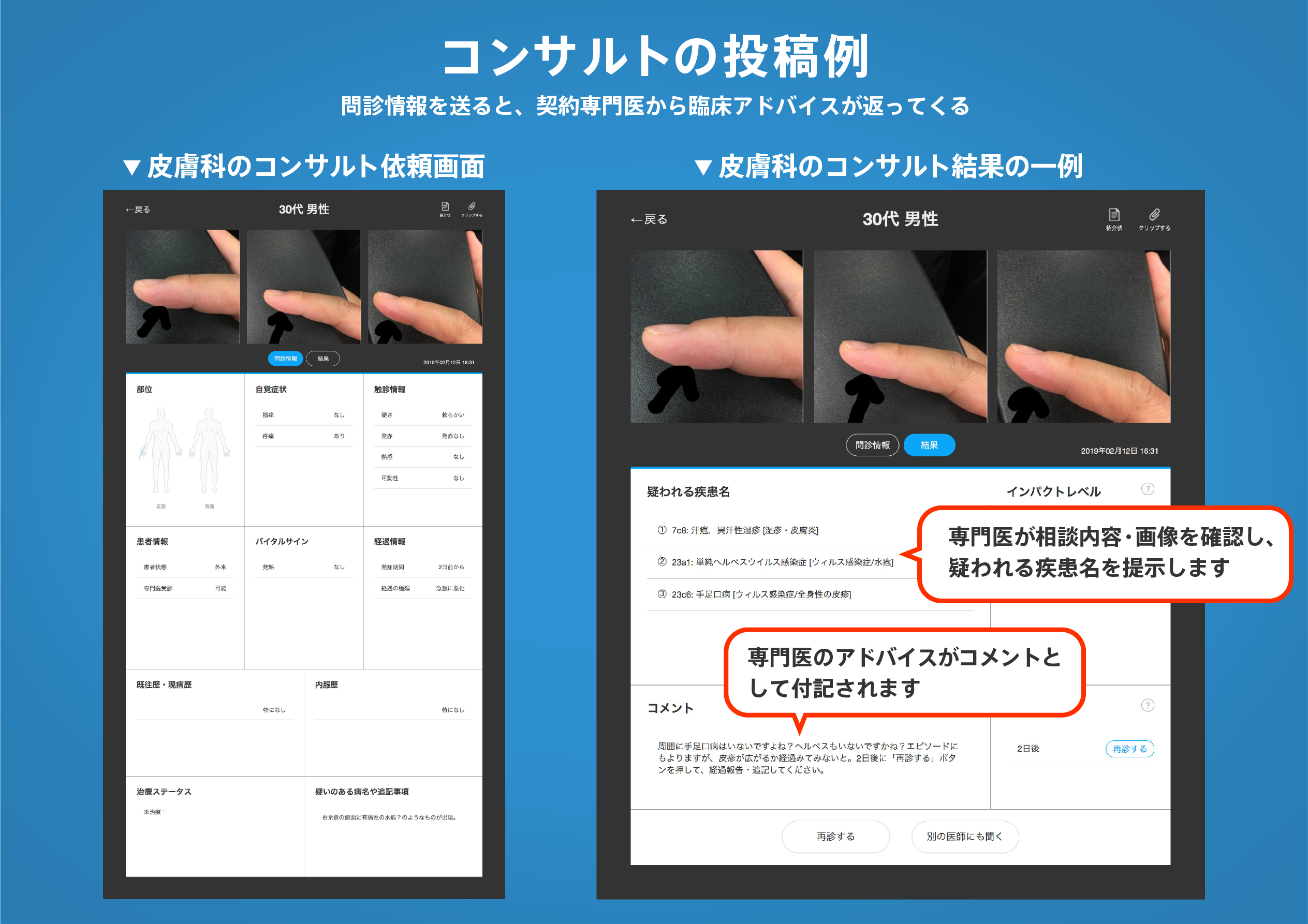

医師のための臨床サポートサービス

ヒポクラ x マイナビのご紹介

無料会員登録していただくと、さらに便利で効率的な検索が可能になります。