著名医師による解説が無料で読めます

すると翻訳の精度が向上します

人工知能は、コンピューティング能力の増加により、過去10年間で多くのアプリケーションを発見しました。人工ニューラルネットワークは、脳構造に触発され、いわゆるディープニューラルネットワーク(DNNS)の人工シナプスを介した人工ニューロンの相互接続で構成されています。これらのシステムのトレーニングには膨大な量のデータが必要であり、ネットワークがトレーニングされた後、予期しないデータを認識し、有用な情報を提供できます。トレーニングに関する限り、監督された学習と教師なしの学習を区別できます。前者はラベル付きデータを必要とし、確率勾配降下法を使用した出力誤差の反復最小化に基づいています。その後、バックプロパゲーションアルゴリズムとのシナプス接続(重み)の強度の再計算が続きます。一方、監視されていない学習はデータのラベル付けを必要とせず、明示的な出力エラーの最小化に基づいていません。従来のANNは、監視された学習アルゴリズム(パーセプトロン、多層パーセプロン、畳み込みネットワークなど)で機能するだけでなく、監視されていない学習ルール(コホネンネットワーク、自己組織化マップなど)でも機能します。それに加えて、別のタイプのニューラルネットワークは、ニューロンによって打ち上げられた電圧スパイクの重ね合わせを通じて学習が行われるいわゆるスパイクニューラルネットワーク(SNN)です。それらの行動は、監視された監視されていない学習ルールで使用できる脳機能のメカニズムにはるかに近いです。学習と推論は短い電圧スパイクに基づいているため、エネルギー効率は大幅に向上します。この瞬間まで、これらすべてのANN(スパイクおよび従来)は、Von Neumannアーキテクチャに基づいて従来のコンピューティングユニットで実行されるソフトウェアツールとして実装されています。ただし、このアプローチは、必要なコンピューティングパワー、物理的なサイズ、エネルギー消費により重要な制限に達します。これは、インターネットの端にあるアプリケーションに特に当てはまります。したがって、このタイプのアプリケーションのために、ハードウェアに直接実装されたAIツールの開発に関心が高まっています。最初のハードウェアのデモンストレーションは、相補的な金属酸化物 - 陰導体(CMOS)回路と特定の通信プロトコルに基づいています。ただし、システムサイズを削減しながらトレーニング速度とエネルギー効率をさらに向上させるために、CMOSニューロン回路とメモリスタシナプスの組み合わせが調査されています。また、一部のメモリスタの短時間の非揮発性は、純粋にメモリスなアンを製造することさえ可能にするかもしれないと指摘されています。Memristorは、記憶を持つ抵抗として動作する新しいデバイス(2008年に固体状態で最初に実証されています)であり、生物学的シナプスと同様の増強とうつ病の特性を持っていることが示されています。この特別号では、AIアプリケーション用のMemristorsを使用してニューラルネットワークを実装する神経モルフィック回路の最先端を探ります。

人工知能は、コンピューティング能力の増加により、過去10年間で多くのアプリケーションを発見しました。人工ニューラルネットワークは、脳構造に触発され、いわゆるディープニューラルネットワーク(DNNS)の人工シナプスを介した人工ニューロンの相互接続で構成されています。これらのシステムのトレーニングには膨大な量のデータが必要であり、ネットワークがトレーニングされた後、予期しないデータを認識し、有用な情報を提供できます。トレーニングに関する限り、監督された学習と教師なしの学習を区別できます。前者はラベル付きデータを必要とし、確率勾配降下法を使用した出力誤差の反復最小化に基づいています。その後、バックプロパゲーションアルゴリズムとのシナプス接続(重み)の強度の再計算が続きます。一方、監視されていない学習はデータのラベル付けを必要とせず、明示的な出力エラーの最小化に基づいていません。従来のANNは、監視された学習アルゴリズム(パーセプトロン、多層パーセプロン、畳み込みネットワークなど)で機能するだけでなく、監視されていない学習ルール(コホネンネットワーク、自己組織化マップなど)でも機能します。それに加えて、別のタイプのニューラルネットワークは、ニューロンによって打ち上げられた電圧スパイクの重ね合わせを通じて学習が行われるいわゆるスパイクニューラルネットワーク(SNN)です。それらの行動は、監視された監視されていない学習ルールで使用できる脳機能のメカニズムにはるかに近いです。学習と推論は短い電圧スパイクに基づいているため、エネルギー効率は大幅に向上します。この瞬間まで、これらすべてのANN(スパイクおよび従来)は、Von Neumannアーキテクチャに基づいて従来のコンピューティングユニットで実行されるソフトウェアツールとして実装されています。ただし、このアプローチは、必要なコンピューティングパワー、物理的なサイズ、エネルギー消費により重要な制限に達します。これは、インターネットの端にあるアプリケーションに特に当てはまります。したがって、このタイプのアプリケーションのために、ハードウェアに直接実装されたAIツールの開発に関心が高まっています。最初のハードウェアのデモンストレーションは、相補的な金属酸化物 - 陰導体(CMOS)回路と特定の通信プロトコルに基づいています。ただし、システムサイズを削減しながらトレーニング速度とエネルギー効率をさらに向上させるために、CMOSニューロン回路とメモリスタシナプスの組み合わせが調査されています。また、一部のメモリスタの短時間の非揮発性は、純粋にメモリスなアンを製造することさえ可能にするかもしれないと指摘されています。Memristorは、記憶を持つ抵抗として動作する新しいデバイス(2008年に固体状態で最初に実証されています)であり、生物学的シナプスと同様の増強とうつ病の特性を持っていることが示されています。この特別号では、AIアプリケーション用のMemristorsを使用してニューラルネットワークを実装する神経モルフィック回路の最先端を探ります。

Artificial Intelligence has found many applications in the last decade due to increased computing power. Artificial Neural Networks are inspired in the brain structure and consist in the interconnection of artificial neurons through artificial synapses in the so-called Deep Neural Networks (DNNs). Training these systems requires huge amounts of data and, after the network is trained, it can recognize unforeseen data and provide useful information. As far as the training is concerned, we can distinguish between supervised and unsupervised learning. The former requires labelled data and is based on the iterative minimization of the output error using the stochastic gradient descent method followed by the recalculation of the strength of the synaptic connections (weights) with the backpropagation algorithm. On the other hand, unsupervised learning does not require data labeling and it is not based on explicit output error minimization. Conventional ANNs can function with supervised learning algorithms (perceptrons, multi-layer perceptrons, convolutional networks, etc.) but also with unsupervised learning rules (Kohonen networks, self-organizing maps, etc.). Besides, another type of neural networks are the so-called Spiking Neural Networks (SNNs) in which learning takes place through the superposition of voltage spikes launched by the neurons. Their behavior is much closer to the brain functioning mechanisms they can be used with supervised and unsupervised learning rules. Since learning and inference is based on short voltage spikes, energy efficiency improves substantially. Up to this moment, all these ANNs (spiking and conventional) have been implemented as software tools running on conventional computing units based on the von Neumann architecture. However, this approach reaches important limits due to the required computing power, physical size and energy consumption. This is particularly true for applications at the edge of the internet. Thus, there is an increasing interest in developing AI tools directly implemented in hardware for this type of applications. The first hardware demonstrations have been based on Complementary Metal-Oxide-Semiconductor (CMOS) circuits and specific communication protocols. However, to further increase training speed andenergy efficiency while reducing the system size, the combination of CMOS neuron circuits with memristor synapses is now being explored. It has also been pointed out that the short time non-volatility of some memristors may even allow fabricating purely memristive ANNs. The memristor is a new device (first demonstrated in solid-state in 2008) which behaves as a resistor with memory and which has been shown to have potentiation and depression properties similar to those of biological synapses. In this Special Issue, we explore the state of the art of neuromorphic circuits implementing neural networks with memristors for AI applications.

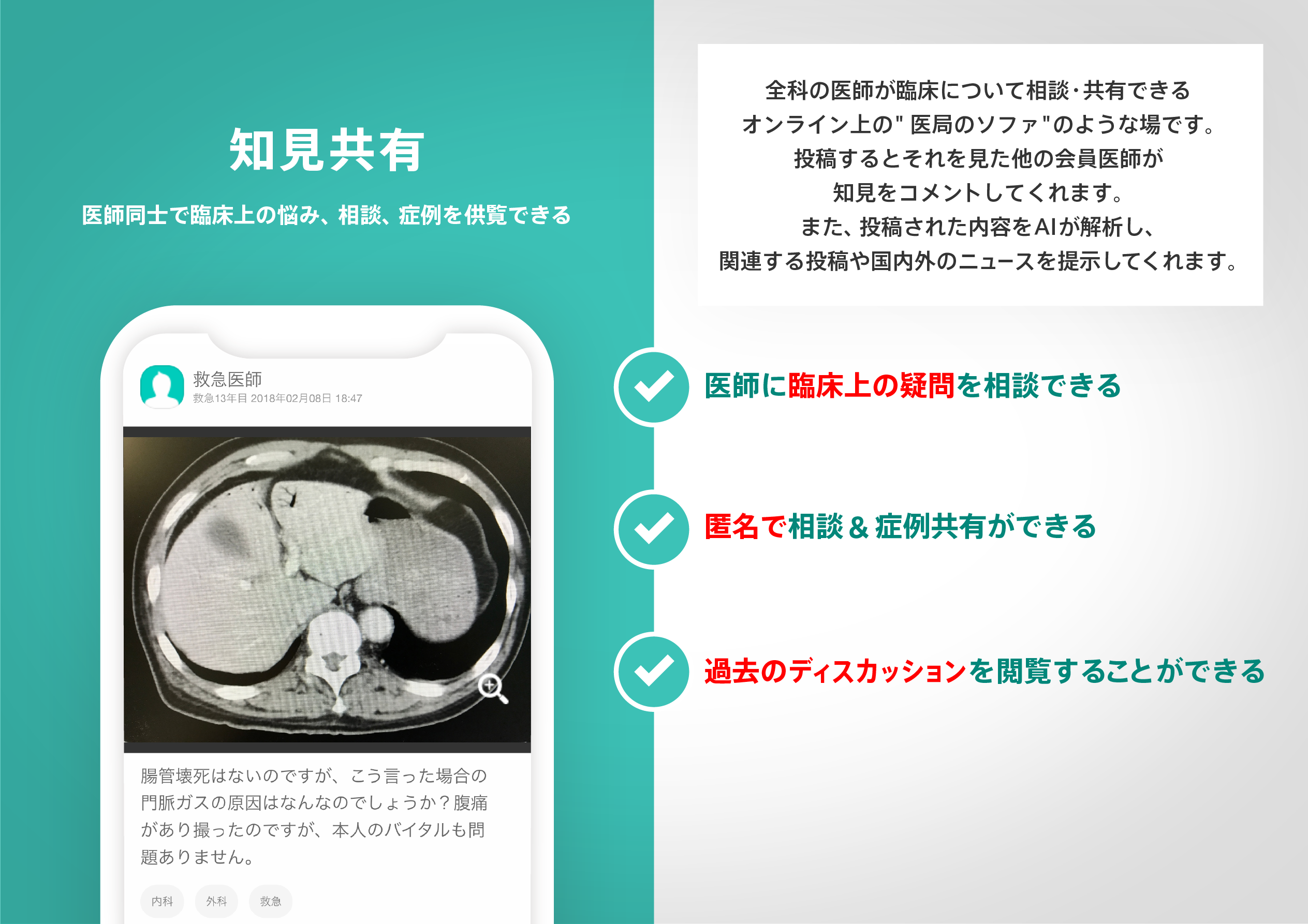

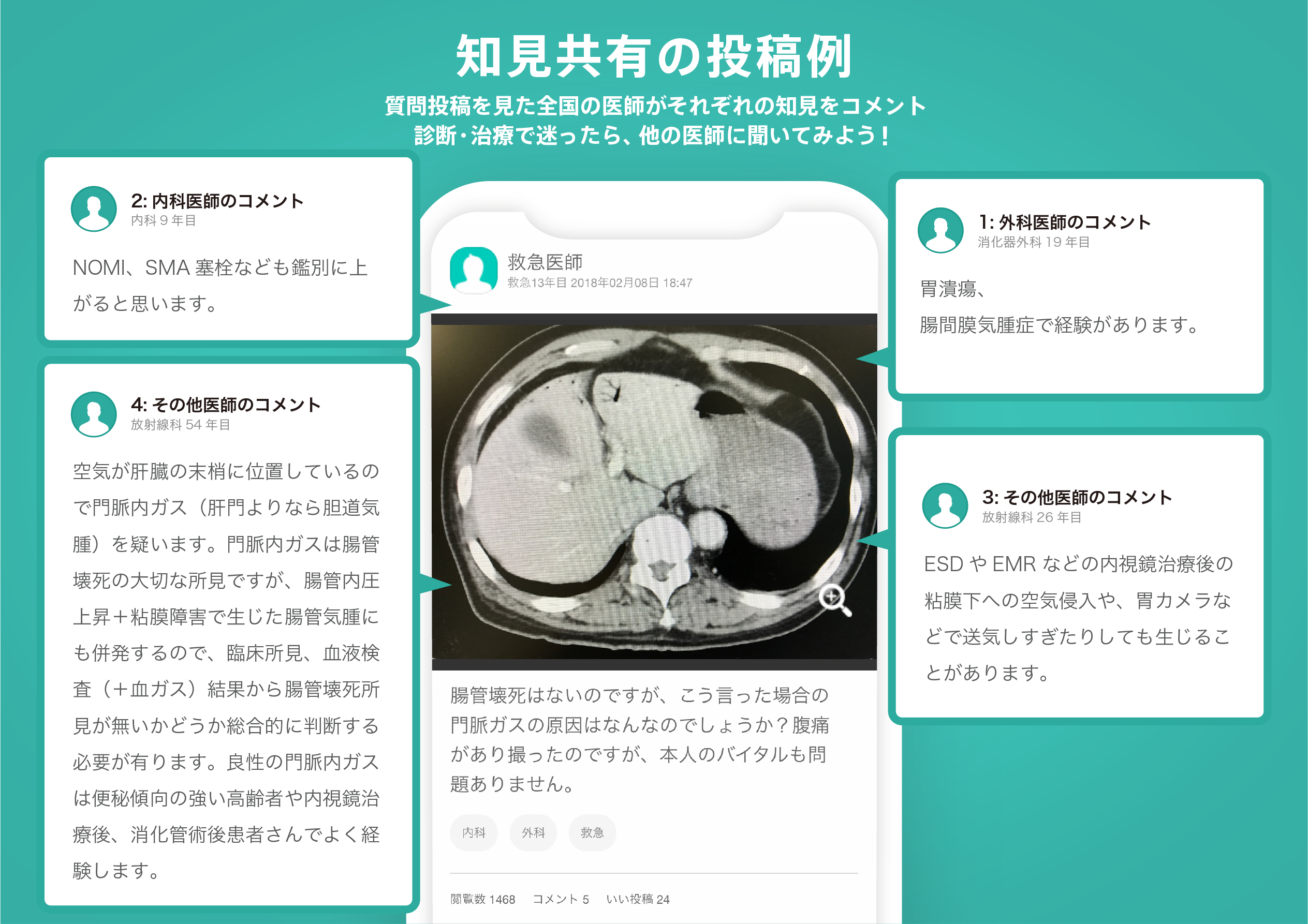

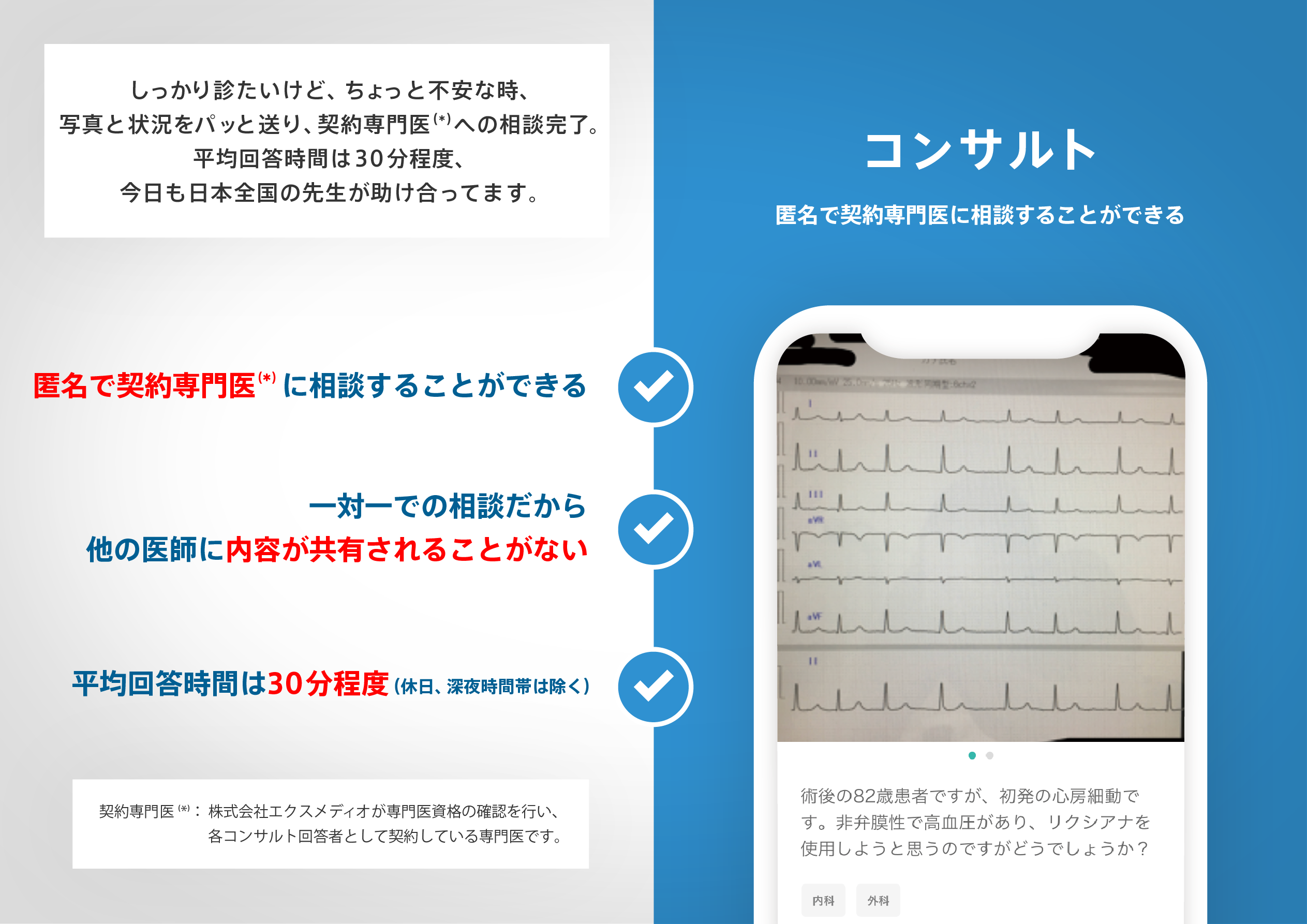

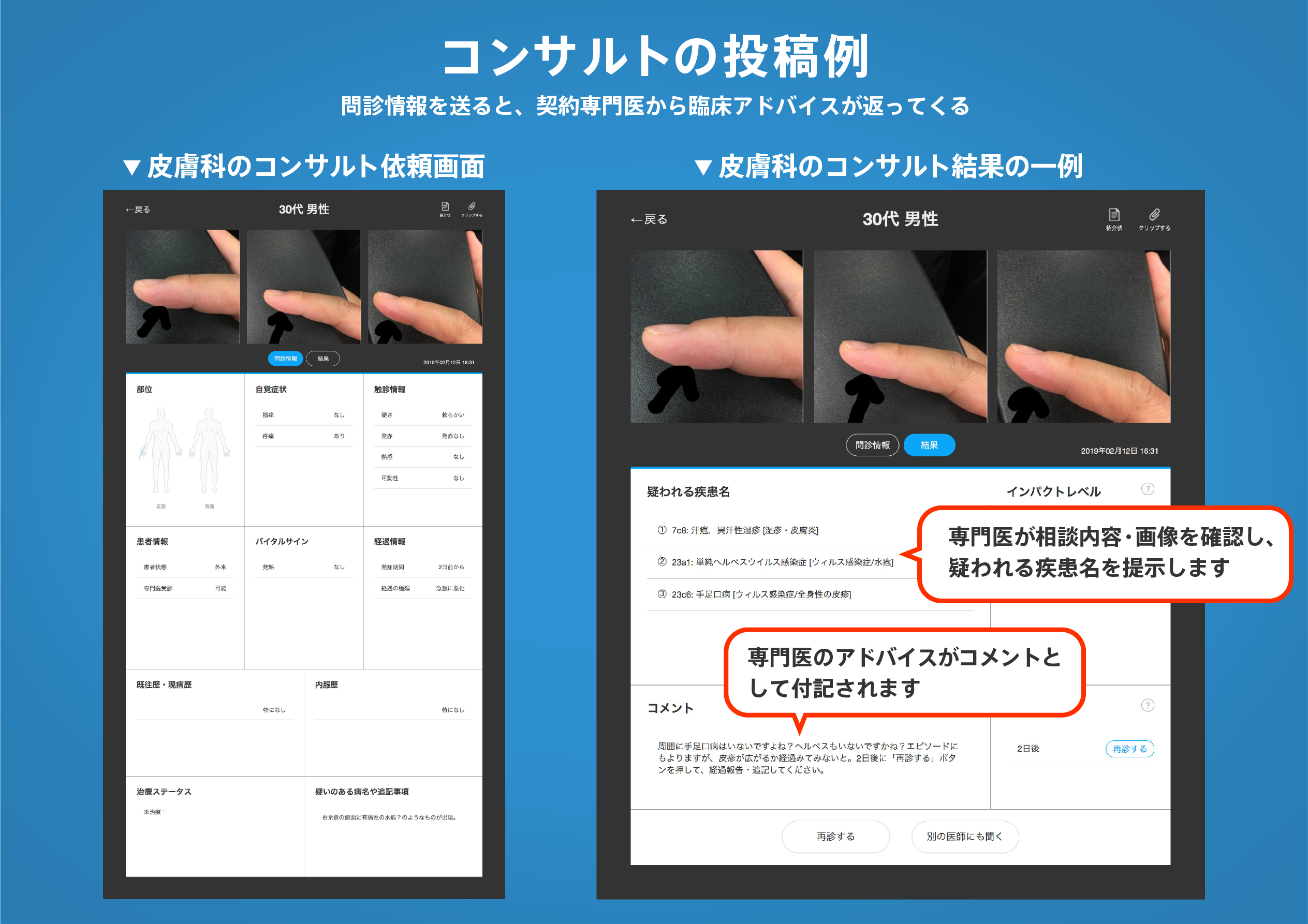

医師のための臨床サポートサービス

ヒポクラ x マイナビのご紹介

無料会員登録していただくと、さらに便利で効率的な検索が可能になります。