著名医師による解説が無料で読めます

すると翻訳の精度が向上します

この論文では、埋め込み動的ランダムアクセスメモリ(EDRAM)マクロのアナログインメモリー(PIM)のマクロの拡張保持時間を備えた擬似静的ゲインセル(PS-GC)を紹介します。提案されているEDRAMセルは、電荷損失の問題なしに保存されたデータを維持する疑似静的漏れ補償を備えた2つのトランジスタ(2T)ゲインセルで構成されています。したがって、PS-GCは、静的RAM(SRAM)と同じ方法で無制限の保持時間を提供できます。保持時間の延長により、従来のEDRAMのかさばるコンデンサはもはや必要ありません。それにより、EDRAMベースのアナログPIMの面積効率が向上します。PS-GCの積極的な漏れ補償は、重大な漏れ電流を示す深層尿道プロセスでも、保存されたデータを効果的に保持できます。したがって、PS-GCは、漏れ電流の増加を懸念なく、書き込みアクセス時間と読み取り時間を加速することができます。提案されたゲインセルとその64×64 EDRAMマクロは、28 nm CMOSプロセスで実装されました。提案されたゲインセルのビットセルは、それぞれ6T SRAMと8T STAMの面積の0.79および0.58倍と0.58倍です。レイアウト後のシミュレーション結果は、EDRAMがプロセス、電圧、温度の広範囲のバリエーションで無制限の保持時間で正常に擬似静的動作を維持していることを示しています。667 MHzの動作周波数では、EDRAMマクロは、プロセスの変動に関係なく、0.9〜1.2 Vの動作電圧範囲と-25〜85°Cの動作温度範囲を達成しました。レイアウト後のシミュレートされた記述時間と読み取りアクセス時間は、85°Cの動作温度で0.3 ns未満でした。PS-GCは、25°Cの動作温度で2.2 nW/ビットの静的出力を消費します。

この論文では、埋め込み動的ランダムアクセスメモリ(EDRAM)マクロのアナログインメモリー(PIM)のマクロの拡張保持時間を備えた擬似静的ゲインセル(PS-GC)を紹介します。提案されているEDRAMセルは、電荷損失の問題なしに保存されたデータを維持する疑似静的漏れ補償を備えた2つのトランジスタ(2T)ゲインセルで構成されています。したがって、PS-GCは、静的RAM(SRAM)と同じ方法で無制限の保持時間を提供できます。保持時間の延長により、従来のEDRAMのかさばるコンデンサはもはや必要ありません。それにより、EDRAMベースのアナログPIMの面積効率が向上します。PS-GCの積極的な漏れ補償は、重大な漏れ電流を示す深層尿道プロセスでも、保存されたデータを効果的に保持できます。したがって、PS-GCは、漏れ電流の増加を懸念なく、書き込みアクセス時間と読み取り時間を加速することができます。提案されたゲインセルとその64×64 EDRAMマクロは、28 nm CMOSプロセスで実装されました。提案されたゲインセルのビットセルは、それぞれ6T SRAMと8T STAMの面積の0.79および0.58倍と0.58倍です。レイアウト後のシミュレーション結果は、EDRAMがプロセス、電圧、温度の広範囲のバリエーションで無制限の保持時間で正常に擬似静的動作を維持していることを示しています。667 MHzの動作周波数では、EDRAMマクロは、プロセスの変動に関係なく、0.9〜1.2 Vの動作電圧範囲と-25〜85°Cの動作温度範囲を達成しました。レイアウト後のシミュレートされた記述時間と読み取りアクセス時間は、85°Cの動作温度で0.3 ns未満でした。PS-GCは、25°Cの動作温度で2.2 nW/ビットの静的出力を消費します。

This paper presents a pseudo-static gain cell (PS-GC) with extended retention time for an embedded dynamic random-access memory (eDRAM) macro for analog processing-in-memory (PIM). The proposed eDRAM cell consists of a two-transistor (2T) gain cell with a pseudo-static leakage compensation that maintains stored data without charge loss issue. Hence, the PS-GC can offer unlimited retention time in the same manner as static RAM (SRAM). Due to the extended retention time, bulky capacitors in conventional eDRAM are no longer needed, thereby, improving the area efficiency of eDRAM-based analog PIMs. The active leakage compensation of the PS-GC can effectively hold stored data even in a deep-submicron process that show significant leakage current. Therefore, the PS-GC can accelerate write-access time and read-access time without concern of increased leakage current. The proposed gain cell and its 64 × 64 eDRAM macro were implemented in a 28 nm CMOS process. The bitcell of the proposed gain cell has 0.79- and 0.58-times the area of those of 6T SRAM and 8T STAM, respectively. The post-layout simulation results demonstrate that the eDRAM maintains the pseudo-static operation with unlimited retention time successfully under wide range variations of process, voltage and temperature. At the operating frequency of 667 MHz, the eDRAM macro achieved an operating voltage range from 0.9 to 1.2 V and operating temperature range from -25 to 85 °C regardless of the process variation. The post-layout simulated write-access time and read-access time were below 0.3 ns at an operating temperature of 85 °C. The PS-GC consumes a static power of 2.2 nW/bit at an operating temperature of 25 °C.

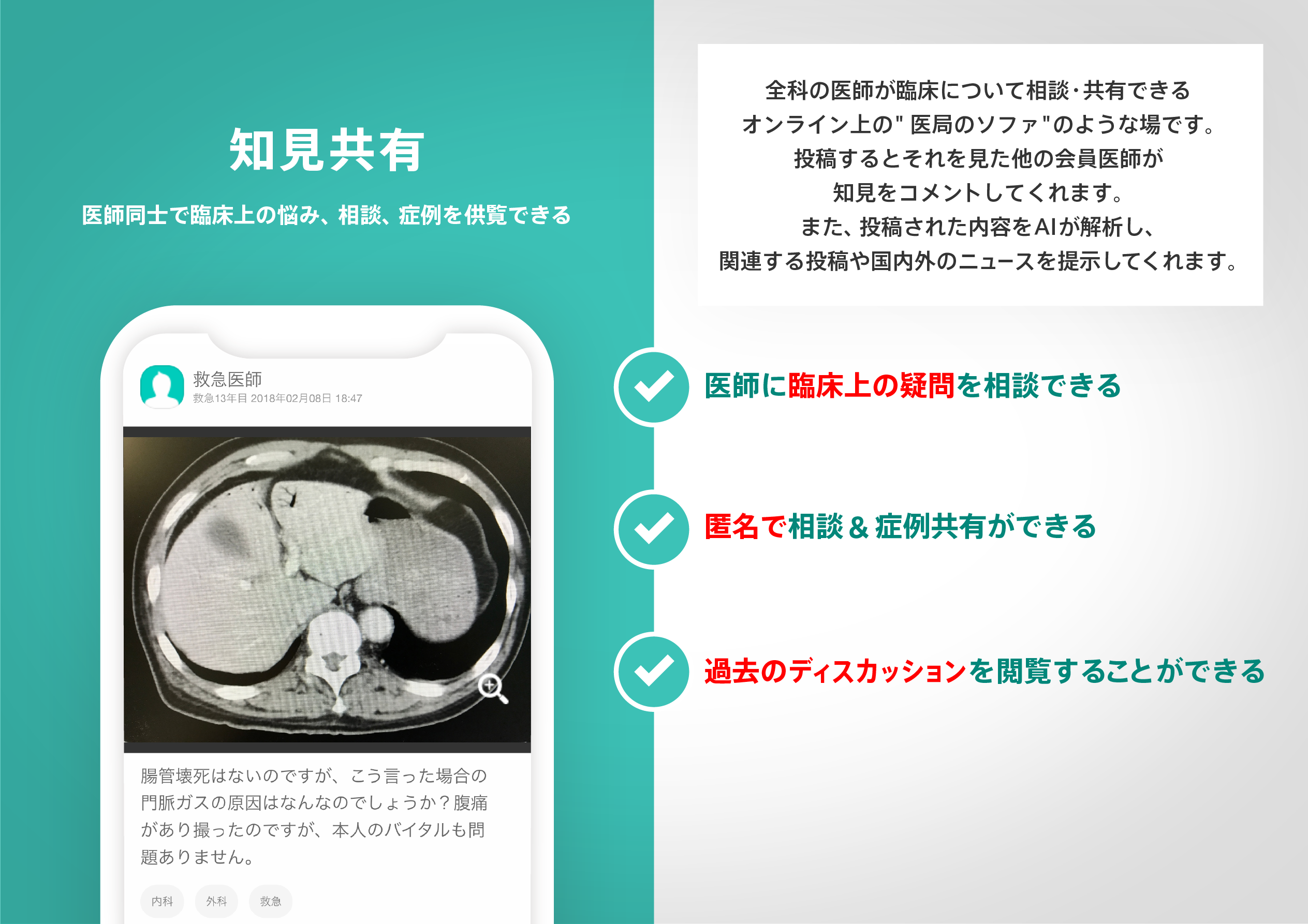

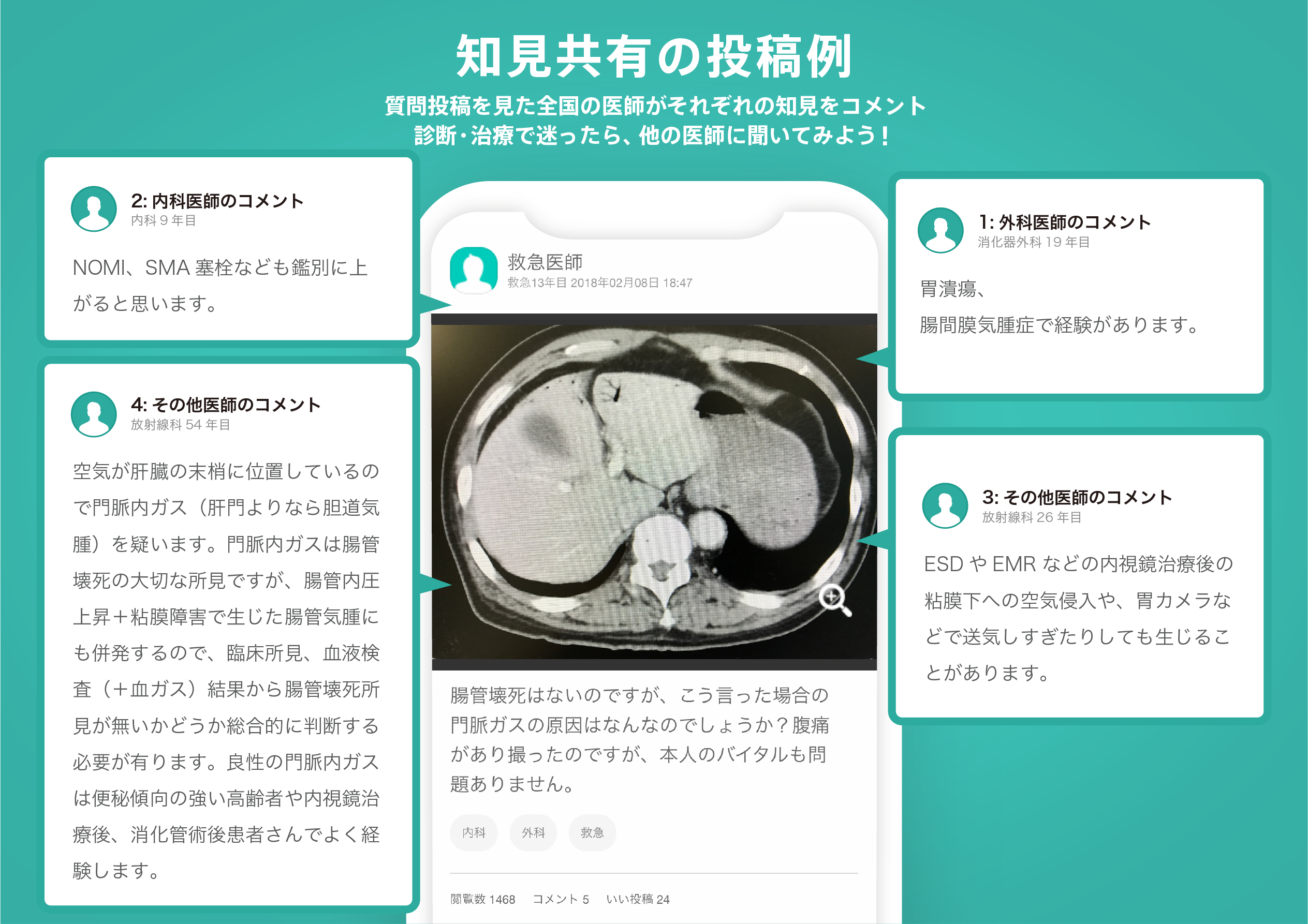

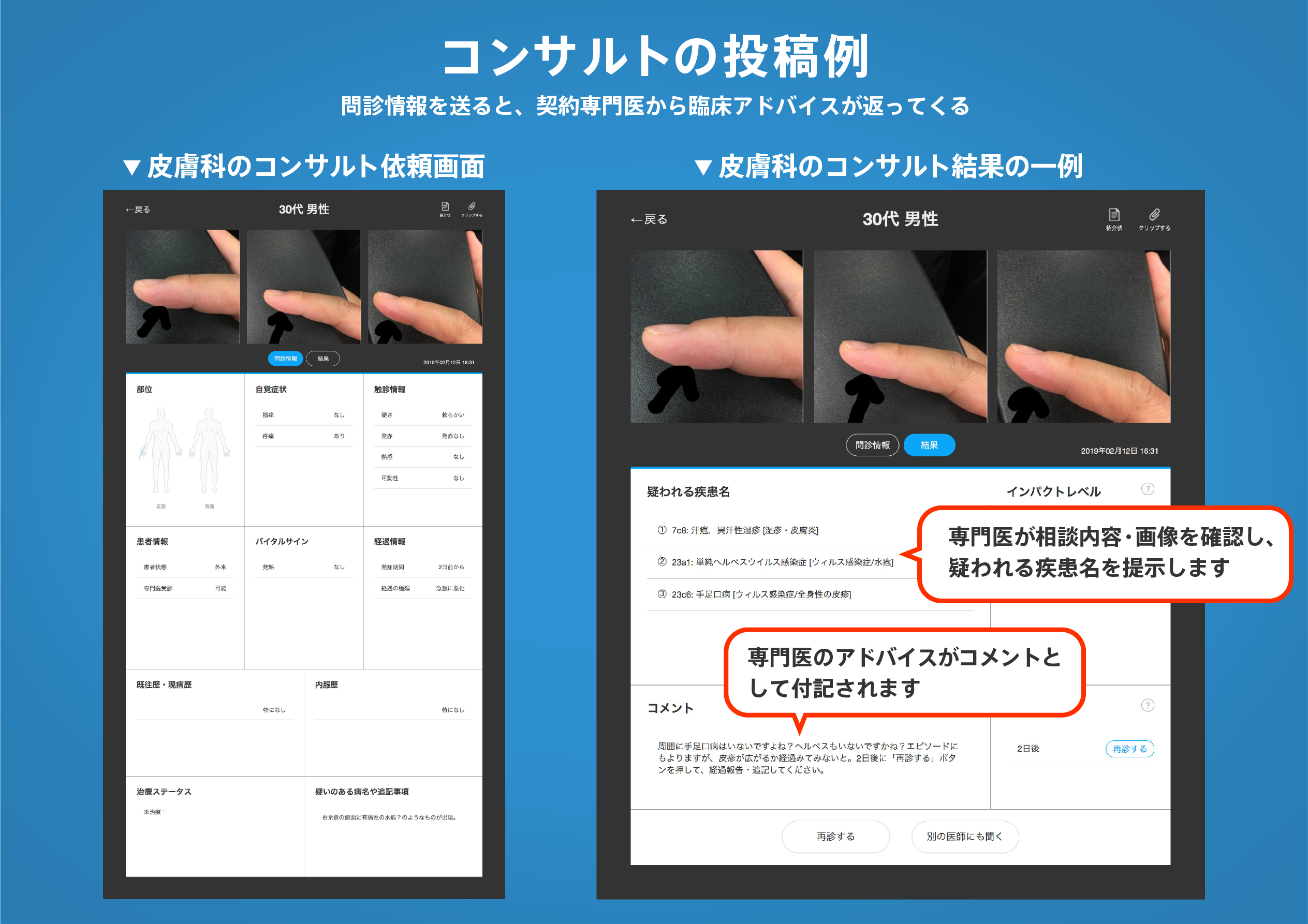

医師のための臨床サポートサービス

ヒポクラ x マイナビのご紹介

無料会員登録していただくと、さらに便利で効率的な検索が可能になります。