著名医師による解説が無料で読めます

すると翻訳の精度が向上します

3次元NANDフラッシュメモリは、高速データアクセスを通じてシステムの安定性を保証する高度なストレージメディアとして、センサーシステムで広く使用されています。ただし、フラッシュメモリでは、セルビットの数が増加し、プロセスピッチがスケーリングを続けると、特に近隣のワードライン干渉(NWI)の場合、データの妨害がより深刻になり、データストレージの信頼性の劣化につながります。したがって、NWIメカニズムを調査し、この長年の扱いにくい問題の重要なデバイス因子を評価するために、物理デバイスモデルが構築されました。TCADによってシミュレートされたように、読み取りバイアス条件下でのチャネルポテンシャルの変化は、実際のNWIパフォーマンスと良好な一貫性を示します。このモデルを使用して、NWIの生成は、潜在的な重ね合わせと局所排水誘発バリア低下(DIBL)効果の組み合わせを通じて正確に説明できます。これは、チャネルポテンシャルによって送信されるより高いビットライン電圧(VBL)が局所的なDIBL効果を回復できることを示唆しています。これはNWIによって弱くなります。さらに、3D NANDメモリアレイには適応性のあるVBL対策が提案されており、すべての状態の組み合わせでトリプルレベルセル(TLC)のNWIを大幅に最小限に抑えることができます。デバイスモデルと適応VBLスキームは、TCADおよび3D NANDチップテストによって正常に検証されました。この研究では、3D NANDフラッシュのNWI関連の問題に関する新しい物理モデルを紹介し、データの信頼性を最適化する対策として実行可能で有望な電圧スキームを提供します。

3次元NANDフラッシュメモリは、高速データアクセスを通じてシステムの安定性を保証する高度なストレージメディアとして、センサーシステムで広く使用されています。ただし、フラッシュメモリでは、セルビットの数が増加し、プロセスピッチがスケーリングを続けると、特に近隣のワードライン干渉(NWI)の場合、データの妨害がより深刻になり、データストレージの信頼性の劣化につながります。したがって、NWIメカニズムを調査し、この長年の扱いにくい問題の重要なデバイス因子を評価するために、物理デバイスモデルが構築されました。TCADによってシミュレートされたように、読み取りバイアス条件下でのチャネルポテンシャルの変化は、実際のNWIパフォーマンスと良好な一貫性を示します。このモデルを使用して、NWIの生成は、潜在的な重ね合わせと局所排水誘発バリア低下(DIBL)効果の組み合わせを通じて正確に説明できます。これは、チャネルポテンシャルによって送信されるより高いビットライン電圧(VBL)が局所的なDIBL効果を回復できることを示唆しています。これはNWIによって弱くなります。さらに、3D NANDメモリアレイには適応性のあるVBL対策が提案されており、すべての状態の組み合わせでトリプルレベルセル(TLC)のNWIを大幅に最小限に抑えることができます。デバイスモデルと適応VBLスキームは、TCADおよび3D NANDチップテストによって正常に検証されました。この研究では、3D NANDフラッシュのNWI関連の問題に関する新しい物理モデルを紹介し、データの信頼性を最適化する対策として実行可能で有望な電圧スキームを提供します。

Three-dimensional NAND flash memory is widely used in sensor systems as an advanced storage medium that ensures system stability through fast data access. However, in flash memory, as the number of cell bits increases and the process pitch keeps scaling, the data disturbance becomes more serious, especially for neighbor wordline interference (NWI), which leads to a deterioration of data storage reliability. Thus, a physical device model was constructed to investigate the NWI mechanism and evaluate critical device factors for this long-standing and intractable problem. As simulated by TCAD, the change in channel potential under read bias conditions presents good consistency with the actual NWI performance. Using this model, NWI generation can be accurately described through the combination of potential superposition and a local drain-induced barrier lowering (DIBL) effect. This suggests that a higher bitline voltage (Vbl) transmitted by the channel potential can restore the local DIBL effect, which is ever weakened by NWI. Furthermore, an adaptive Vbl countermeasure is proposed for 3D NAND memory arrays, which can significantly minimize the NWI of triple-level cells (TLC) in all state combinations. The device model and the adaptive Vbl scheme were successfully verified by TCAD and 3D NAND chip tests. This study introduces a new physical model for NWI-related problems in 3D NAND flash, while providing a feasible and promising voltage scheme as a countermeasure to optimize data reliability.

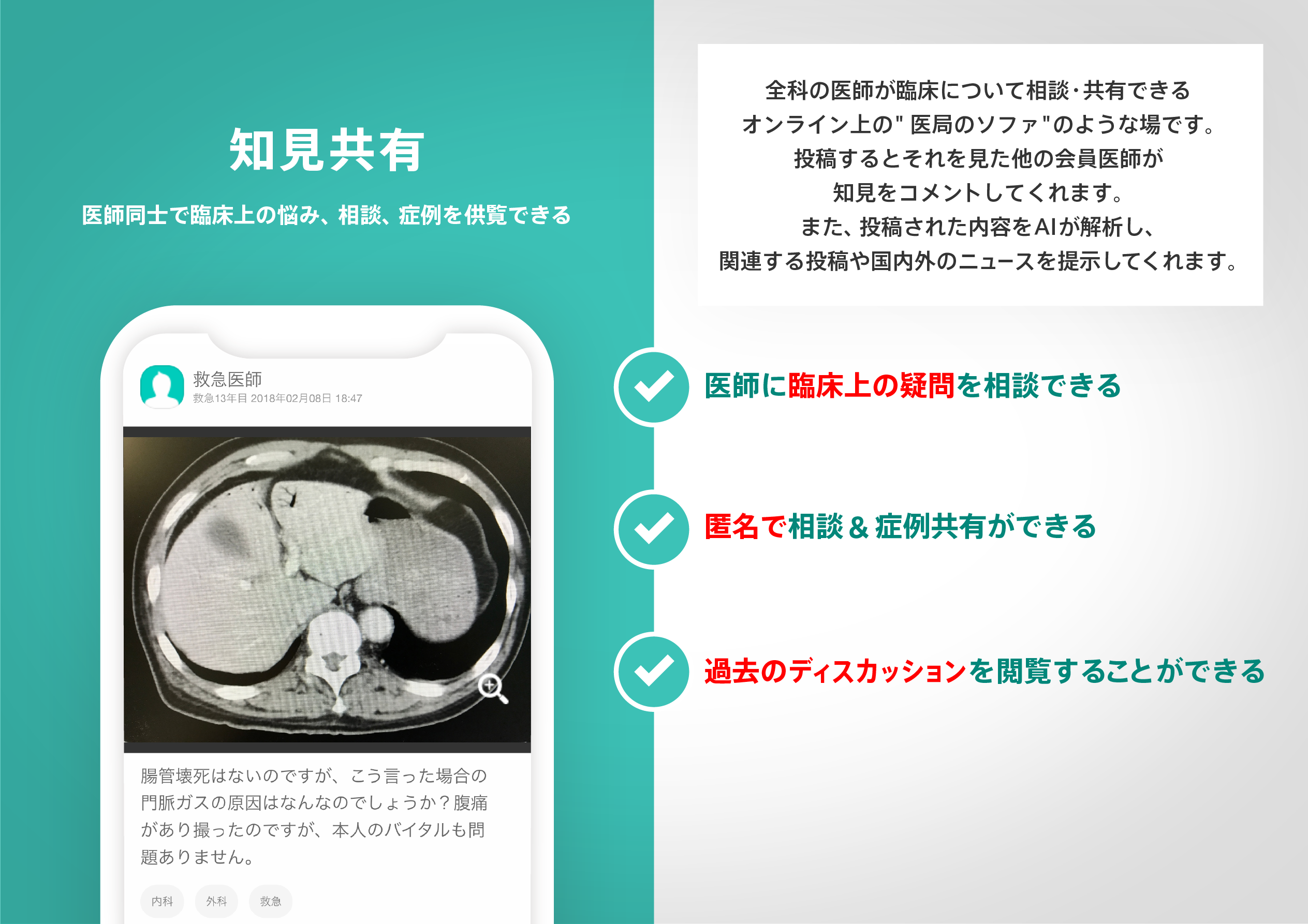

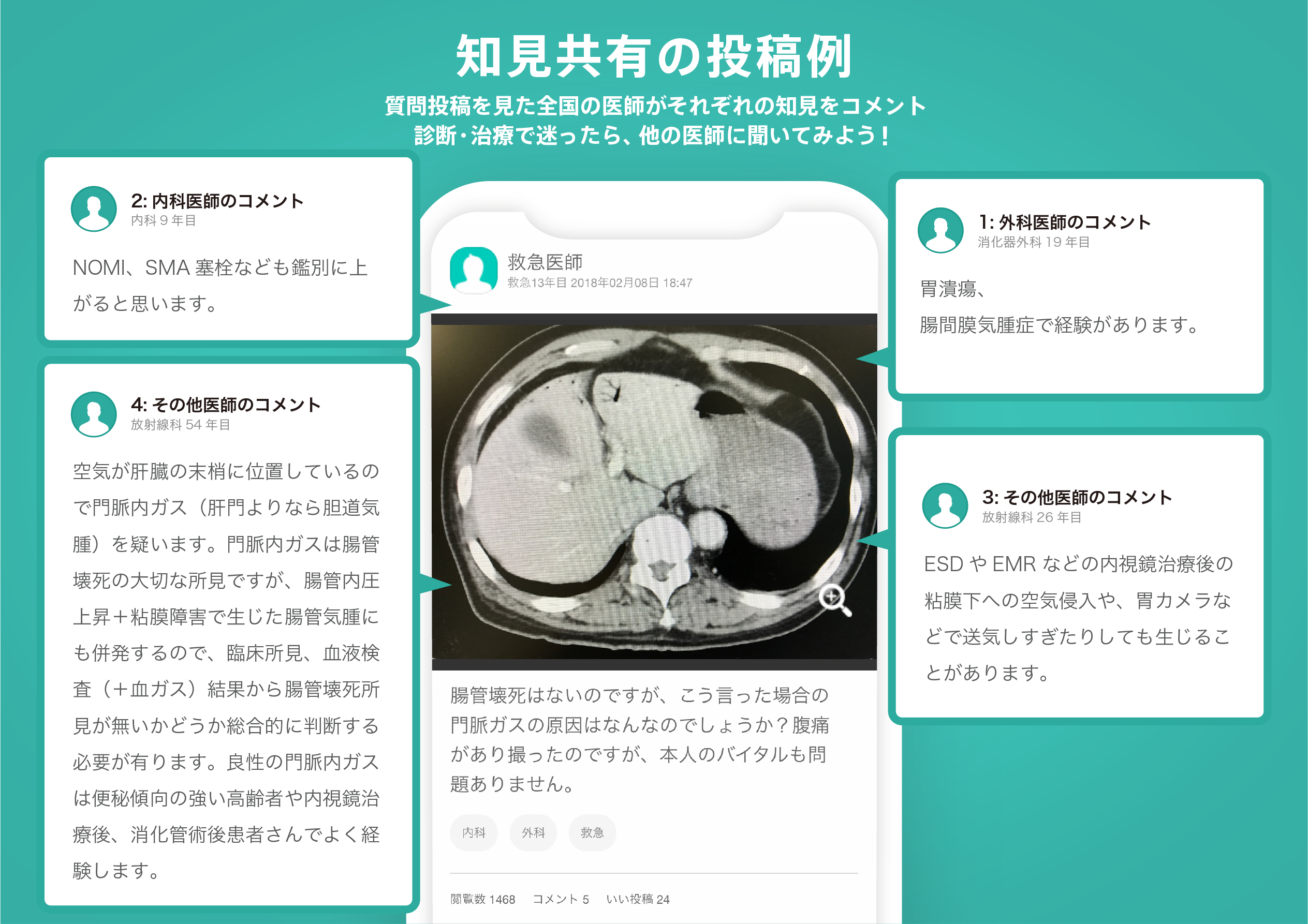

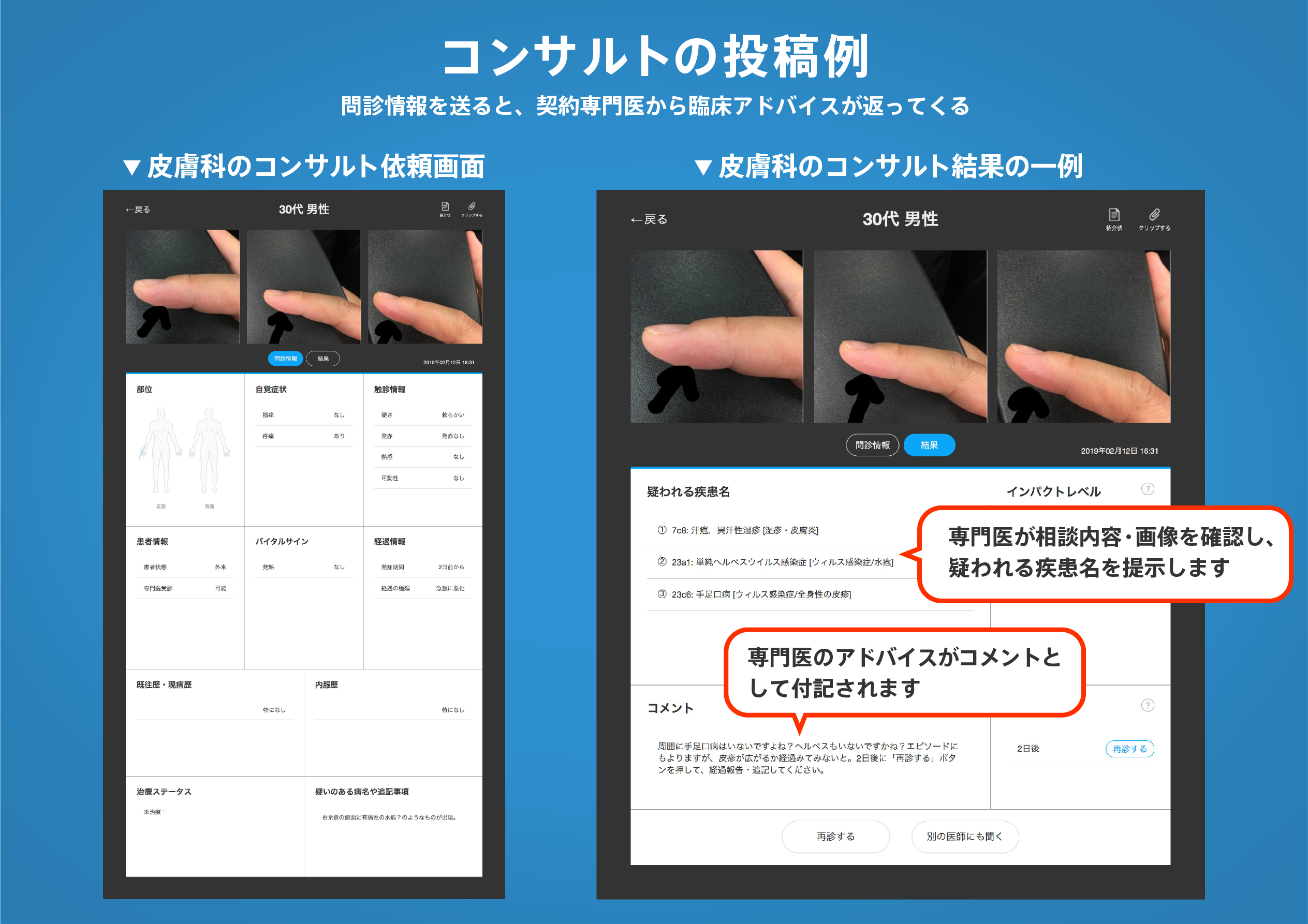

医師のための臨床サポートサービス

ヒポクラ x マイナビのご紹介

無料会員登録していただくと、さらに便利で効率的な検索が可能になります。